NEO半导体准备学习3D NAND堆叠闪存制造512GB内存条 采用3D X-DRAM进行堆叠

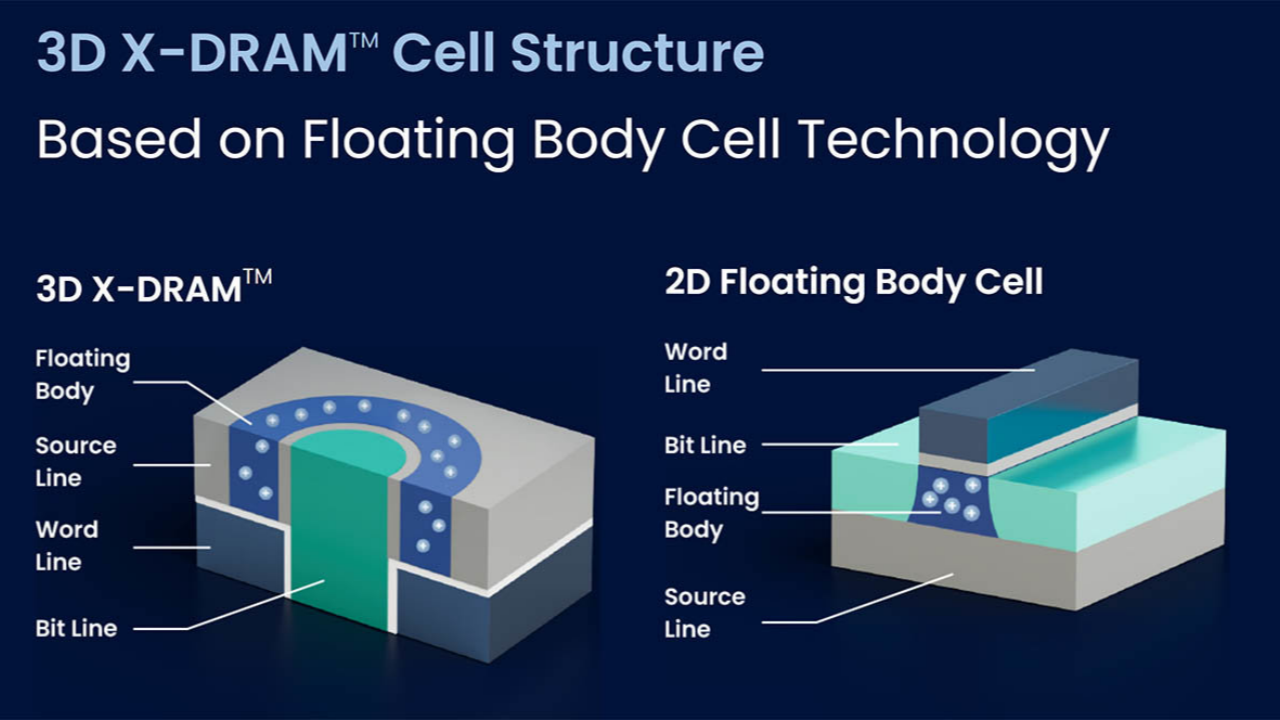

半导体公司 NEO Semiconductor 日前宣布使用 3D X-DRAM 技术在人工智能和高性能计算时代对内存进行重新设计,3D X-DRAM 是模仿存储行业的 3D NAND 闪存,将芯片进行垂直多层堆叠以提高密度和性能。

NEO 半导体承诺堆叠层可以大幅度提高存储容量、增强带宽和降低功耗,其技术方案是通过垂直狭缝分成多个扇区,并且字线层通过阶级结构连接 (也就是垂直堆叠架构的样式)。

与当前 0A 节点的平面 48GB DRAM 相比,NEO 半导体称其 3D X-DRAM 架构可以让内存条达到 512GB,这类超大容量的内存条在人工智能计算和高性能计算领域可能有一定的需求。

不过当前 NEO 半导体的概念验证芯片还处在早期阶段,NEO 目前正在开发更简单的 1T0C 架构测试版本,而更加复杂且更有前进的 1T1C 版本计划在 2026 年 推出,该版本采用 IGZO (铟镓锌氧) 薄膜晶体管搭配圆柱形高 k 介电电容,有望将数据保留时间提升到 450 秒且可以堆叠 128 层,未来的 3T0C 设计则会采用双 IGZO 层,主要面向内存计算和 AI 应用。

当然这些超大容量内存短时间内是肯定不会面向消费者市场推出的,且不说价格肯定非常高昂,消费者硬件里也不会支持单条 512GB 这种大容量内存条,所以在 NEO 半导体开发成功后也需要与硬件制造商合作,至少要上服务器硬件率先支持才行。